- 您现在的位置:买卖IC网 > Sheet目录321 > DK-START-3C25N (Altera)KIT STARTER CYCLONE III EP3C25

�� �

�

�

�1–26�

�Chapter� 1:� Cyclone� III� Device� Datasheet�

�I/O� Timing�

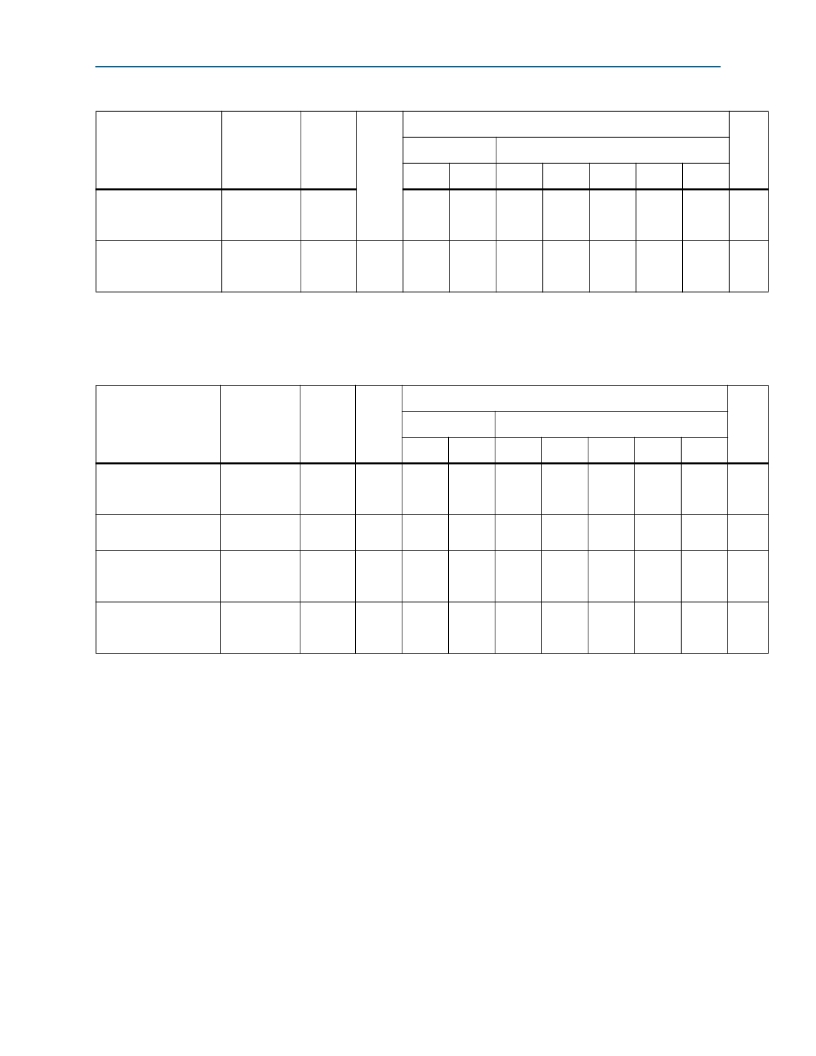

�Table� 1–37.� Cyclone� III� Devices� IOE� Programmable� Delay� on� Column� Pins� (1)� ,�

�(2)�

�(Part� 2� of� 2)�

�Max� Offset�

�Parameter�

�Paths�

�Affected�

�Number�

�of�

�Settings�

�Min�

�Offset�

�Fast� Corner�

�Slow� Corner�

�Unit�

�A7,� I7�

�C6�

�C6�

�C7�

�C8�

�I7�

�A7�

�Delay� from� output�

�register� to� output� pin�

�I/O� output�

�register� to�

�pad�

�2�

�0�

�0.479�

�0.504�

�0.915�

�1.011�

�1.107�

�1.018�

�1.048�

�ns�

�Input� delay� from�

�Pad� to� global�

�dual-purpose� clock� pin�

�clock�

�12�

�0�

�0.664�

�0.694�

�1.199�

�1.378�

�1.532�

�1.392�

�1.441�

�ns�

�to� fan-out� destinations�

�network�

��(1)� The� incremental� values� for� the� settings� are� generally� linear.� For� exact� values� of� each� setting,� use� the� latest� version� of� the� Quartus� II� software.�

�(2)� The� minimum� and� maximum� offset� timing� numbers� are� in� reference� to� setting� ‘0’� as� available� in� the� Quartus� II� software.�

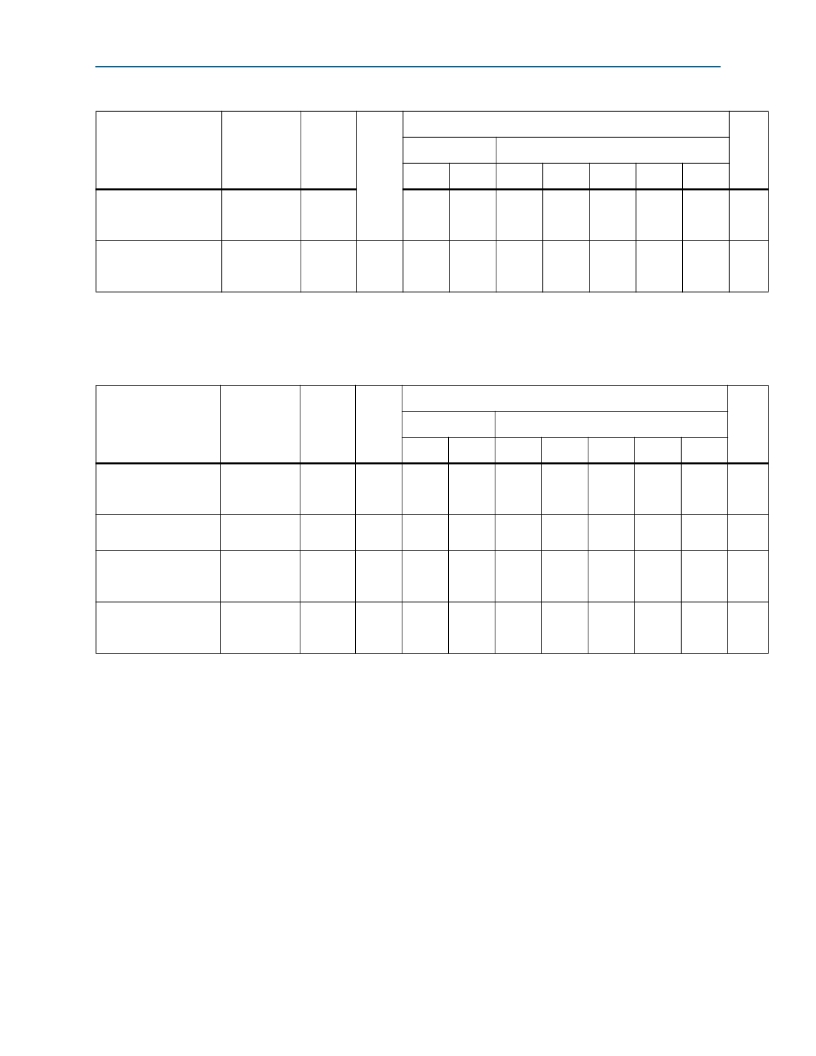

�Table� 1–38.� Cyclone� III� Devices� IOE� Programmable� Delay� on� Row� Pins�

��Max� Offset�

�Parameter�

�Paths�

�Affected�

�Number�

�of�

�Settings�

�Min�

�Offset�

�Fast� Corner�

�Slow� Corner�

�Unit�

�A7,� I7�

�C6�

�C6�

�C7�

�C8�

�I7�

�A7�

�Input� delay� from� pin� to�

�internal� cells�

�Input� delay� from� pin� to�

�input� register�

�Delay� from� output�

�register� to� output� pin�

�Input� delay� from�

�dual-purpose� clock� pin�

�to� fan-out� destinations�

�Pad� to� I/O�

�dataout� to�

�core�

�Pad� to� I/O�

�input� register�

�I/O� output�

�register� to�

�pad�

�Pad� to� global�

�clock� network�

�7�

�8�

�2�

�12�

�0�

�0�

�0�

�0�

�1.209�

�1.207�

�0.51�

�0.669�

�1.314�

�1.312�

�0.537�

�0.698�

�2.174�

�2.202�

�0.962�

�1.207�

�2.335�

�2.402�

�1.072�

�1.388�

�2.406�

�2.558�

�1.167�

�1.542�

�2.381�

�2.447�

�1.074�

�1.403�

�2.505�

�2.557�

�1.101�

�1.45�

�ns�

�ns�

�ns�

�ns�

��(1)� The� incremental� values� for� the� settings� are� generally� linear.� For� exact� values� of� each� setting,� use� the� latest� version� of� Quartus� II� software.�

�(2)� The� minimum� and� maximum� offset� timing� numbers� are� in� reference� to� setting� ‘0’� as� available� in� the� Quartus� II� software�

�I/O� Timing�

�You� can� use� the� following� methods� to� determine� the� I/O� timing:�

�■�

�■�

�the� Excel-based� I/O� Timing.�

�the� Quartus� II� timing� analyzer.�

�The� Excel-based� I/O� Timing� provides� pin� timing� performance� for� each� device� density�

�and� speed� grade.� The� data� is� typically� used� prior� to� designing� the� FPGA� to� get� a�

�timing� budget� estimation� as� part� of� the� link� timing� analysis.� The� Quartus� II� timing�

�analyzer� provides� a� more� accurate� and� precise� I/O� timing� data� based� on� the� specifics�

�of� the� design� after� place-and-route� is� complete.�

���July� 2012� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DK-START-4CGX15N

KIT STARTER CYCLONE IV GX

DK-V5-EMBD-ML507-G-J

DEV KIT V5 W/ISM & EDK JAPAN

DK-V6-EMBD-G-XP1

DEV KIT EMBEDDED VIRTEX 6

DK-VIDEO-2C70N

VIDEO KIT W/CYCLONE II EP2C70N

DK-VIDEO-4SGX230N

VIDEO KIT STRATIX IV EP4SGX230

DKUSB-1

KIT DEV FOR MB86065

DLD101-7

IC LED DRIVER HP CONST CURR 8DFN

DLP-2232H-PSOC5

MODULE PSOC5 USB ADAPTER FT2232H

相关代理商/技术参数

DK-START-4CGX15N

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For EP4CGX15BF14

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-START-4CGX15N/P

制造商:Altera Corporation 功能描述:KIT STARTER CYCLONE IV GX TRX PROMO

DK-START-5AGXB3N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For 5AGXFB3H4F35C5N

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-START-5AGXB3NES

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For 5AGXFB3H4F

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DKTA-620

功能描述:测试配件 - 其他 DUAL TYPE K THERMOCOUPLE ADAPTER

RoHS:否 制造商:Tektronix 附件类型:Soft Case 颜色:Gray 设备类型:Transit Case 产品:Accessories

DKTFM3CMA6207

制造商:AVX Corporation 功能描述:

DKTGALL-KIT

功能描述:RS/USB/JTAG/HILOKITS RoHS:否 类别:套件 >> 其它 系列:- 标准包装:1 系列:- 套件类型:照明 套件包括:各类 包装:Digi-Reel® 其它名称:ZXLGMRKIT16DKR

DKTGHILOTEST-KIT

功能描述:TESTER - ADVANCED HIGH LOW RoHS:否 类别:套件 >> 其它 系列:- 标准包装:1 系列:- 套件类型:照明 套件包括:各类 包装:Digi-Reel® 其它名称:ZXLGMRKIT16DKR